Verilog is not a programming language!

SystemVerilog is not a programming language!

(Here programming language means conventional software which typically executes on a processor.)

VHDL, Verilog and SystemVerilog languages are referred to as Hardware Description Languages (HDLs). HDL is a textual description of hardware (i.e. a digital logic circuit).

HDL syntax includes textual description definitions for input, output pins, wires, registers, logic gates and connections between various pins and blocks. If it was software language, why would it include such syntax?

These languages include synthesisable subset that is used to describe digital logic circuit and non-synthesisable subset which is used for hardware verification.

Often behavioural reference models are implemented using the non-synthesisable subset. This subset is also referred to as Hardware Verification Language (HVL), for example SystemVerilog and ‘e’. HVLs are out-of-the scope of this article.

This article is written to inform and educate all those students, engineers, leaders and managers who do not quite appreciate the difference between what happens when a piece of code is written for FPGA implementation in one of the above industry standard HDLs and code written in a programming language to be compiled into an executable that gets executed on a processor.

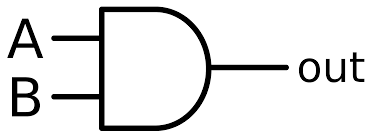

Let us take a very simple example of an “AND” operation with two inputs and one output.

VHDL:

out <= A AND B;

Verilog and SystemVerilog:

assign out = A & B;

C/C++:

out = A & B;

For the sake of argument we will consider FPGA and ASIC implementation principally the same. In the next article we will discuss the differences in more detail.

If we synthesise (not compile) the VHDL, Verilog and SystemVerilog code, it would realise into the following logic gate inside the ASIC/FPGA and not an executable file:

[Image source: https://lalacomputersci.wordpress.com/and-gate/]

This gate is actually realised using CMOS transistors as shown below:

[Image source: https://www.design-reuse.com/articles/38749/efficient-logic-optimization-utilizing-complementary-behavior-of-cmos-gates.html]

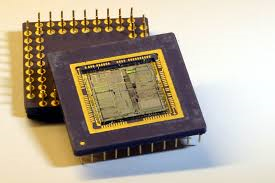

These transistors are etched onto a silicon chip, example shown below:

[Image Source: https://www.freeimages.com/photo/silicon-chip-with-die-1564477]

However, if we compile (not synthesise) the C code it would realise into an executable file which contains binary instructions that can be executed on a target processor. The flow of execution would be like the following if we hand-compile the code into pseudo assembly language:

Move operand A into an accumulator register

Move operand B into an accumulator register

Perform A & B operation into the processor accumulator

Move the result out to a register

Do you see any similarity between the output of a HDL and a Programming language except the logical function?

The HDL code realises into a digital logic circuit which is hardware not software!

Just because the digital logic circuit inside a FPGA can be re-configured at run time, in the field, does not mean it is software!

Treating a HDL for FPGA implementation like software or a programming language is a biggest mistake one can make. Such a mistake can have a direct impact on the project planning in the form of overly optimistic effort estimates for someone in a leading position.

For someone who is starting out, this mistake in their understanding can make them implement the design that may not realise/synthesise into intended hardware or a logic circuit.